# CALCOLATORI ELETTRONICI B – 23 giugno 2009

|                                                      |                 |              |

|------------------------------------------------------|-----------------|--------------|

| <b>NOME:</b>                                         | <b>COGNOME:</b> | <b>MATR:</b> |

| Scrivere chiaramente in caratteri maiuscoli a stampa |                 |              |

1. Si consideri il seguente frammento di codice MIPS:

```

add $s1, $s1, $s0

lw $s0, 20($s1)

sub $s0, $s0, $s0

lw $s0, 20($s2)

sw $s0, 40($s1)

```

Si consideri l'implementazione con pipeline a 5 stadi (F: Fetch, D: Decode, E: Execute, M: Mem, W: Write-Back). Si chiede di:

- a) individuare in modo preciso tutte le dipendenze tra i dati

b) tracciare il diagramma temporale delle istruzioni (indicando esplicitamente le eventuali propagazioni e, per ognuna di esse, quale dato è propagato) in ognuna delle seguenti ipotesi:

- non è disponibile alcuna unità di propagazione

- è disponibile un'unità di propagazione verso lo stadio E

- è disponibile un'unità di propagazione verso lo stadio E ed una verso lo stadio M.

Nei diagrammi, si chiede di indicare il numero di cicli di penalità. [6]

2. Si consideri un processore MIPS, implementato tramite pipeline a 5 stadi, che disponga di una cache primaria e di una cache secondaria (distinte per i dati e le istruzioni). La cache primaria presenta le seguenti caratteristiche:

- numero di cicli di clock richiesti in caso di successo (hit): 1

- percentuale di successo (hit rate): 80% per le istruzioni, 70% per i dati

- penalità di fallimento: 8 cicli di clock

Per la cache secondaria valgono invece le seguenti condizioni:

- percentuale di successo (hit rate): 90% per le istruzioni, 80% per i dati

- cicli di clock per trasferire un blocco dalla cache secondaria alla cache primaria: 3

Si assuma un carico di lavoro che prevede la seguente distribuzione delle istruzioni MIPS:

|         |      |

|---------|------|

| lw:     | 20 % |

| sw:     | 20 % |

| Tipo-R: | 30 % |

| beq:    | 20 % |

| j:      | 10 % |

Si supponga inoltre che:

- il 40% delle istruzioni Tipo-R siano seguite da istruzioni che ne utilizzano il risultato;

- il 10% delle istruzioni lw siano seguite da istruzioni Tipo-R che ne utilizzano il risultato;

- il 10% delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato solo per il calcolo dell'indirizzo;

- il 20% delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato solo per immagazzinarlo in memoria;

- il 5% delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato sia per il calcolo dell'indirizzo sia per immagazzinarlo in memoria

Tenendo conto dei miss di cache e delle criticità sui dati, si calcoli il CPI (numero medio di cicli di clock per istruzione) ottenuto nei due casi seguenti:

- si dispone di un'unità di propagazione solo verso lo stadio E

- si dispone di un'unità di propagazione verso lo stadio E ed una verso lo stadio M. [4]

3. In qualità di esperti consulenti dell'implementazione del processore MIPS mediante pipeline a 5 stadi, vi viene chiesto di esprimere un parere rispetto alla possibilità di implementare le istruzioni Tipo-R in modo che l'operazione logico-aritmetica venga effettuata nel quarto stadio anziché nel terzo. Ciò naturalmente richiederebbe di aggiungere una ALU nel quarto stadio, mentre quella al terzo stadio verrebbe usata solo per il calcolo dell'indirizzo delle istruzioni di accesso alla memoria. In tal modo si risolverebbero tutte le criticità sui dati che danno luogo a stallo, ovvero quelle carica-e-usa (*lw* seguita da *Tipo-R* che ne utilizza il risultato)!!! Si chiede di esprimere un parere articolato in merito alla proposta. [2]

4. Nell'ambito delle tecniche di controllo con pipeline, si illustri brevemente (max 5-6 righe) la differenza tra tecniche di predizione statica e dinamica dei salti.

Si consideri una tecnica di previsione dinamica realizzata mediante un automa a due stati: si discuta la gestione dei cicli mediante questa soluzione precisando (riferendosi ad un ciclo ripetuto n volte) i miglioramenti che si possono ottenere con l'adozione di un automa a quattro stati. [3]

5. Si consideri un calcolatore in cui la cache della memoria centrale utilizza la tecnica di write back (è presente un dirty bit per ciascun blocco). Per ciascuno dei seguenti due casi, si dica se e quali interventi devono essere effettuati nella cache per assicurare la coerenza dei dati:

- a seguito di un page fault, una pagina fisica in memoria centrale viene rimpiazzata da una nuova pagina fisica caricata dal disco;

- il processo corrente esaurisce il suo tempo di utilizzo del processore e viene sostituito da un nuovo processo. [3]

6. Si consideri il seguente frammento di codice MIPS (i puntini indicano la presenza di un certo numero di istruzioni non specificate):

```

add $t0, $s1, $s2

beq $t0, $t1, Dest

sub $s1, $s3, $s4

add $s4, $s4, $s2

...

Dest: ...

```

Si consideri un'implementazione con pipeline a 4 stadi (Fetch – Decode – Execute – Write Back) dotata di una coda delle istruzioni e con le seguenti caratteristiche:

- la coda può contenere 4 istruzioni, che l'unità di prelievo è in grado di caricare contemporaneamente in un solo ciclo di clock;

- i salti condizionati vengono eseguiti da un'apposita sotto-unità dell'unità di prelievo (Fetch), parallelamente all'esecuzione delle istruzioni negli altri stadi;

- per i salti condizionati, si utilizza un BTB (in grado di predire la condizione e la destinazione del salto) che in questo caso ha previsto che il salto sia effettuato

- l'hardware rende possibile la propagazione dei dati verso l'unità di prelievo delle istruzioni.

Si chiede di:

- tracciare i diagrammi temporali nei due casi in cui la predizione per la beq sia corretta ed errata (assumere che le quattro istruzioni del frammento di codice siano caricate insieme nella coda delle istruzioni)

- determinare in entrambi i casi la penalità di salto. [4]

7. Considerando il TLB e la tabella delle pagine riportate di seguito, si supponga che siano generati i seguenti due indirizzi virtuali:

0000000000000001 00000001

0000000000000011 11111111

Per ciascun indirizzo, si dica se esso genera un hit o miss di TLB e di pagina; si individui inoltre, se possibile, il corrispondente indirizzo fisico generato. Infine, si dica se e come il TLB viene modificato in seguito alla generazione dei due indirizzi. [3]

**TLB**

| bit di<br>validità | Numero di pagina virtuale | Numero di pagina<br>fisica |

|--------------------|---------------------------|----------------------------|

| 1                  | 0000000000000010          | 10000000                   |

| 1                  | 0000000000000011          | 11111111                   |

| 1                  | 00000000000000100         | 00000000                   |

| 0                  | 00000000000000111         | 11100000                   |

**Tabella delle pagine**

| bit di<br>validità |          |

|--------------------|----------|

| 1                  | 11111001 |

| 1                  | 11111000 |

| 1                  | 10000000 |

| 1                  | 11111111 |

| 1                  | 00000000 |

| 0                  | .        |

| 0                  | .        |

| .                  | .        |

| .                  | .        |

| 0                  | .        |

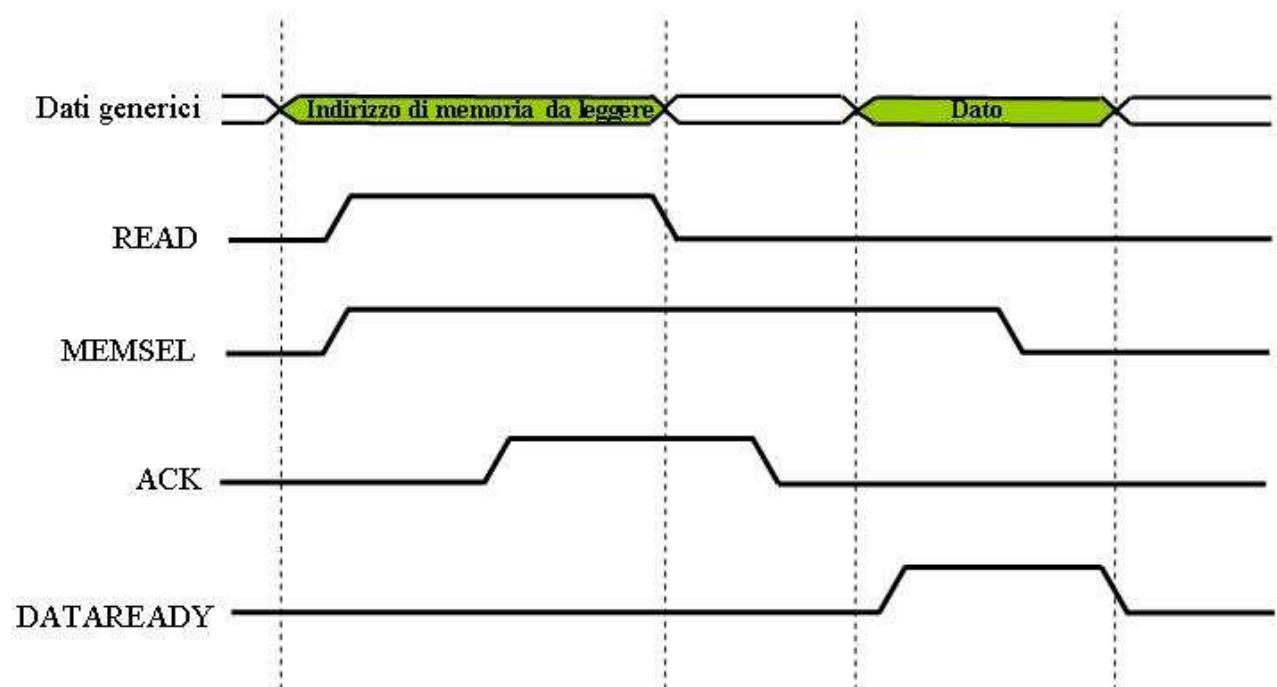

8. E' dato un bus asincrono che collega un processore P e diversi dispositivi, tra cui la memoria. Il bus è costituito da n linee dati, utilizzate per la trasmissione sia dei dati che degli indirizzi (bus multiplexato) e dalle linee di controllo seguenti:

READ: utilizzato dal processore per segnalare una richiesta di lettura da un dispositivo.

MEMSEL: utilizzato dal processore per segnalare una richiesta di accesso alla memoria.

ACK: segnale di riscontro (acknowledgement) usato dal dispositivo.

DATAREADY: segnale usato per segnalare quando un dato è disponibile sul bus.

Tutti i segnali di controllo sono attivi a livello alto.

La figura seguente riporta l'evoluzione temporale di un'operazione di trasferimento di una parola da un dispositivo (per esempio la memoria) a P (lettura).

Si chiede di:

- Illustrare le relazioni tra i segnali del diagramma precedente, con riferimento al protocollo di handshaking ed alle relazioni di causa-effetto che intercorrono tra i segnali stessi.

- Specificare la macchina a stati finiti che controlla l'esecuzione, nel processore (master), del protocollo di handshaking in lettura illustrato nel precedente diagramma.

- Specificare la macchina a stati finiti che controlla l'esecuzione, nel dispositivo (slave), del protocollo di handshaking in lettura illustrato nel precedente diagramma.

[5]